Software-Defined Vehicle Platform

Open SDV platform for standardized, secure and flexible vehicle architectures with dynamic homologation

The Software Defined Vehicle Platform provides a unified, open, and hardware-independent foundation for modern vehicle software. It combines secure, modular software components with a standardized execution environment – reproducible, portable, and updatable throughout the entire lifecycle.

Through open interfaces, isolated runtime environments, integrated shadow mode validation, and formal safety mechanisms, the platform becomes the foundation for scalable, cross-manufacturer SDV architectures.

Open & Standardized

Wasm Component Model, language-independent WIT interfaces, consistent interoperability.

Secure & Isolated

Sandbox runtime, Freedom from Interference, automated safety evidence up to ASIL D.

Hardware Agnostic

x86, ARM, RISC-V, GPU, FPGA – identical binaries from simulation to the vehicle.

Dynamically Certifiable

Component-level homologation, selective OTA updates, shorter release cycles.

From Domains to Central Computers

The vehicle’s E/E architecture is evolving from decentralized domain ECUs through zonal controllers to central high-performance computers. The OSxCAR platform supports every stage of this evolution – and enables mixed operation of classic and SDV-based components.

“One platform for all generations – from legacy ECUs to L3+ central computers.”

01 – Open & Standardized Architecture

The platform is built on open standards such as the WebAssembly Component Model and language-independent interfaces (WIT). This creates consistent interoperability between software building blocks – regardless of programming language, operating system, or hardware.

Components can be freely combined, versioned, reused, or replaced, reducing integration costs and accelerating innovation.

Proprietary stacks create dependencies. WIT + Component Model decouple manufacturer, language, and platform – every component becomes exchangeable, every interface versionable.

02 – Secure, Isolated Execution

Memory-safe runtime environments and sandbox mechanisms ensure that components run strictly isolated from one another (Freedom from Interference). This enables the secure execution of both safety-critical functions and experimental or AI-based modules – without endangering the overall system.

- Memory Safety: No uncontrolled access between modules – capability-based isolation

- Fault Isolation: A module crash remains locally contained, the overall system keeps running

- Safety Evidence: Automated evidence generation for certification processes up to ASIL D

- Formal Verification: Planned mechanisms from component to overall system

Isolation as a Safety Principle

Each component runs in its own sandbox with minimal permissions. Memory access, system calls, and communication channels are strictly controlled – a fault in Module A can never affect Module B.

“Freedom from Interference – not as a concept, but as a runtime guarantee.”

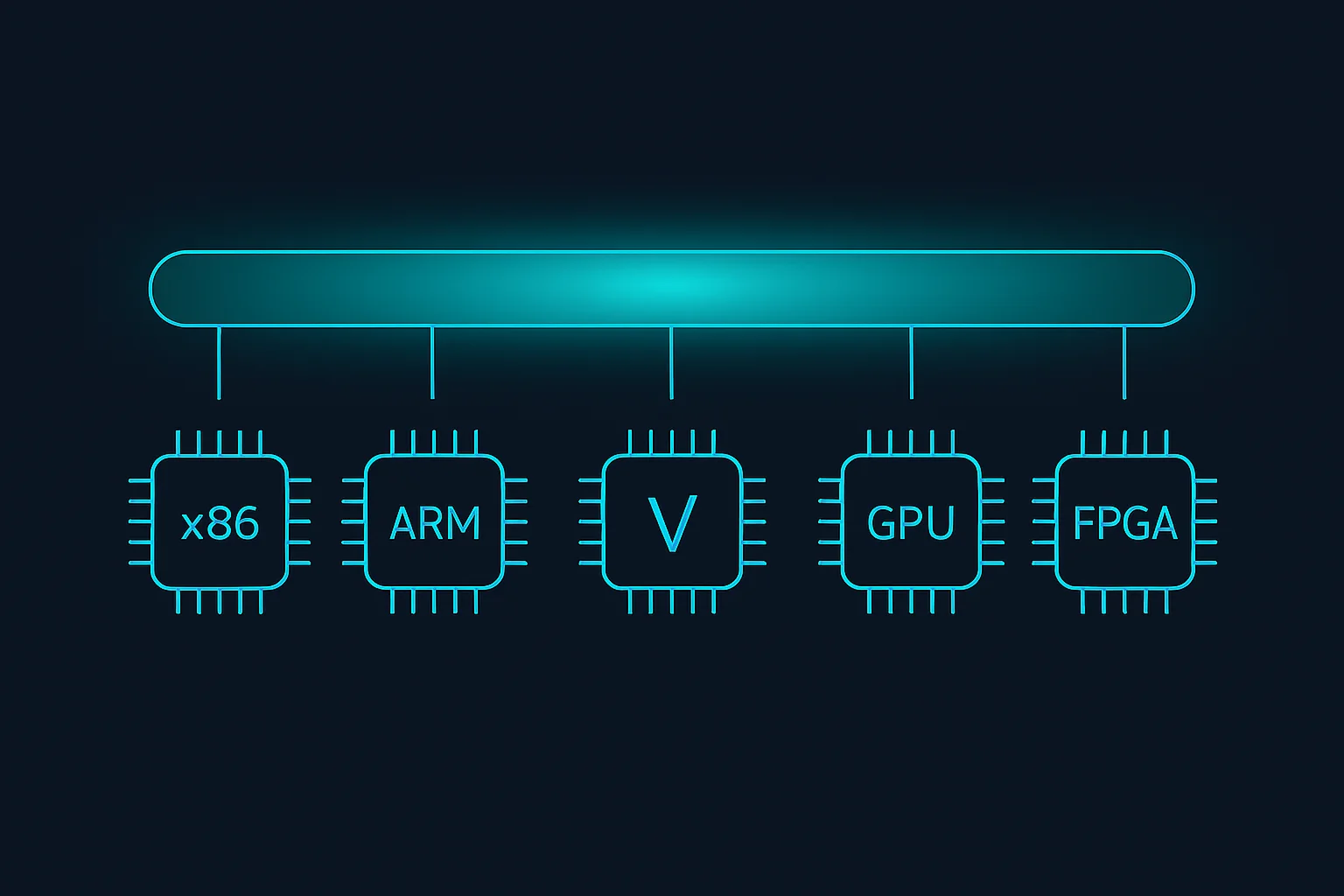

03 – Flexible & Hardware Agnostic

The platform supports all relevant compute architectures – x86, ARM, RISC-V, MCUs, GPUs, FPGAs, and domain-specific accelerators.

Thanks to the “One Binary” approach, identical software modules run across all validation stages:

- MIL / SIL: Early validation purely in simulation – without hardware

- HIL: Real ECUs with simulated signals – real timing, controlled environment

- VIL: Integration in the vehicle context – physical interfaces, real bus systems

- On-Vehicle: Identical code in the target vehicle – developed once, runs everywhere

One Binary – All Platforms

Whether x86 server, ARM-based zone controller, or RISC-V microcontroller – the compiled Wasm component remains identical. No recompile, no platform-specific glue code.

“Developed once, runnable everywhere – from simulation to test bench to vehicle.”

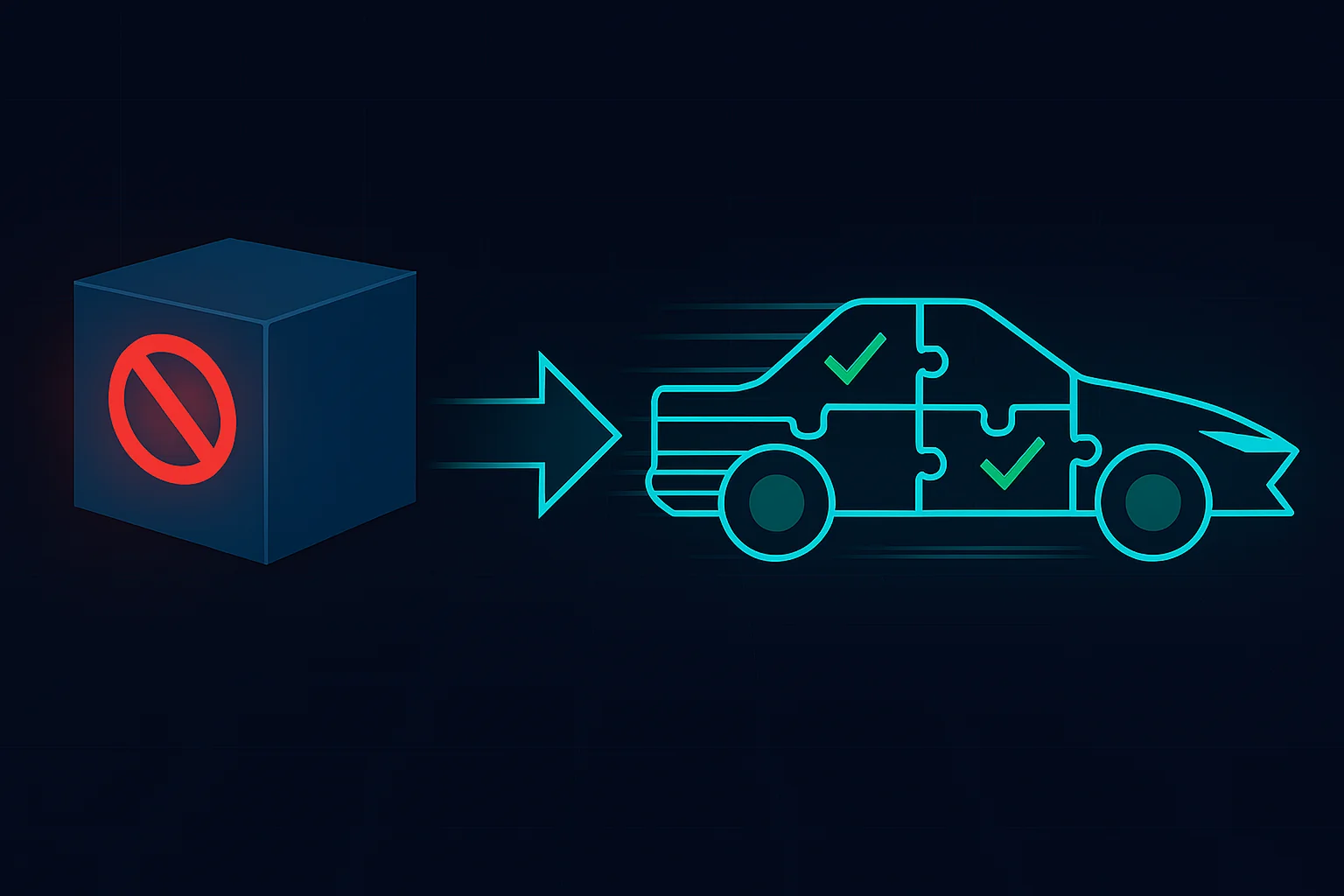

04 – Dynamic Homologation

Instead of recertifying the entire vehicle software, individual components can be selectively updated and reassessed. Dynamic homologation thus becomes the key to SDV lifecycles.

- Selective: Only changed components are reassessed – the rest remains certified

- Fast: Feature rollouts in weeks instead of months

- Efficient: Lower certification costs per release cycle

- Flexible: Low-risk OTA updates and continuous architecture evolution

From Monolith to Module

Classic homologation requires recertification of the entire system with every change. Dynamic homologation breaks this process apart: only the actually changed component is reassessed – the rest remains certified.

“Component-level certification enables feature rollouts in weeks instead of months.”

05 – Shadow Mode – In-Vehicle Validation

New features run in parallel with production logic, receiving real vehicle data and generating comparison outputs without interfering with vehicle functions. Shadow Mode bridges the gap between lab tests and the real vehicle world.

- Fleet Validation: Testing under real conditions across thousands of vehicles

- A/B Testing: Risk-free comparison of new algorithms against production logic

- Data-Driven Optimization: Real driving data as the basis for iterative improvement

- OTA Preparation: Secure validation before productive rollout

From Lab to Fleet

What works on the SDVA Test Bench is finally assured in Shadow Mode under real fleet conditions. New algorithms run in parallel with production – risk-free validation across thousands of vehicles before a single OTA update goes live.

“Feature rollouts in weeks instead of months – selectively updated, component-level certified.”

06 – Roadmap – Future Extensions

The platform’s further development focuses on five priorities: Introduction of formal methods and automated safety analysis for the highest safety requirements. The goal is end-to-end, tool-supported evidence generation from component level to the overall system – as the basis for certification of safety-critical SDV functions. End-to-end evaluation of complex ADAS systems from simulation to driving operation. Re-simulation enables the replay of real scenarios in a controlled environment – for reproducible, scalable validation. Signed, versioned, and modular OTA updates for scalable SDV fleets. Component-level updates instead of monolithic releases – with integrated rollback, audit trail, and dynamic homologation. GNN-based optimization of latency, path selection, and software placement in heterogeneous vehicle networks. Trained on real bench data, validated in Shadow Mode. Demonstration of a fully portable, secure, and OEM-agnostic execution environment based on the WebAssembly Component Model. Proof of practical viability for automotive use cases.Safety Formal Proof Towards ASIL D

Testing ReSim + End-to-End Test Framework for ADAS

Deployment Fleet-Ready OTA Path

AI AI-Optimized Networking

Outlook WebAssembly Proof of Concept

Fleet Updates, Not Solo Missions

Signed, versioned OTA packages reach thousands of vehicles simultaneously. Component-level updates instead of monolithic releases – with integrated rollback, audit trail, and dynamic homologation as safeguards.

“From cloud build to vehicle – continuously signed, versioned, and traceable.”

Suitable for Every E/E Architecture

Whether legacy domain architecture, zonal topology, or central high-performance computers – the platform flexibly adapts to every vehicle generation and enables mixed operation of classic and SDV-based components. Decentralized ECUs separated by function: Powertrain, Chassis, Infotainment. Proven, widely deployed – the platform integrates seamlessly. Regionally grouped controllers by vehicle area. Reduced wiring, higher efficiency – the transition to software-defined architecture. Highly integrated platforms for L3+ autonomy. All functions centralized, maximum computing power – the future of E/E architecture.Legacy Domains

Zone Controllers

Central Computers

In Brief

The SDV platform creates a foundation where:

- Modularity: Software is secure, reusable, and independently combinable

- Portability: Hardware is no longer a barrier – one binary for all target platforms

- Agility: Homologation works dynamically and at the component level

- Intelligence: AI and ReSim are directly integrated into development and validation

- Speed: OTA, Shadow Mode, and safety automation drastically shorten release cycles

A modern, open foundation for the next-generation Software Defined Vehicle.

More Technology Pages: Artificial Intelligence · WebAssembly · Test Platform